Synopsys和臺積電最新萬億晶體管多芯片封裝技術正逐步接近目標

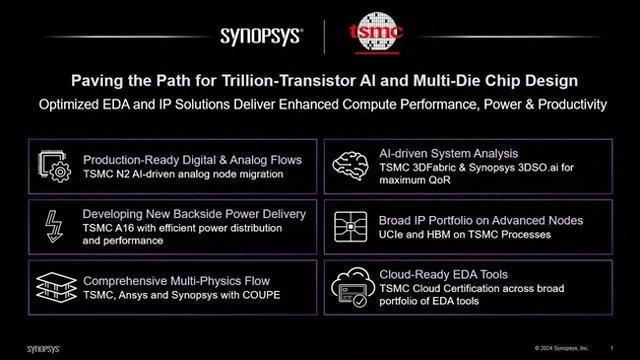

Synopsys 和臺積電已經合作了數十年,一項新的聲明顯示,他們正在將合作關係提升到新的水平,以滿足對更多人工智能計算能力的需求。 Synopsys 透露,該公司正在將其人工智能驅動的 EDA 套件和多芯片解決方案與臺積電的最新工藝節點和 3D 封裝技術緊密結合。 其目標是爲數十億甚至上萬億個晶體管的設計鋪平道路。

EDA 是電子設計自動化(Electronic Design Automation)的縮寫。 它是一套用於設計集成電路芯片等電子系統的軟件工具。 在這方面,Synopsys 針對臺積電N2節點認證的定製設計和仿真工具已經爲聯發科帶來了紅利。

據聯發科的 Ching San Wu 稱,人工智能增強型 EDA 流程使其模擬設計人員能夠在 N2 上最大限度地提高性能和效率,同時加快向市場交付 SoC 的時間。

Synopsys 還宣佈其物理驗證和實施解決方案現在支持臺積電 A16 工藝的背面佈線。 A16 是臺積電有史以來最先進的工藝節點,計劃於 2026 年下半年量產。 背面佈線是一種新興技術,它將電源線佈線在芯片或集成電路的背面,而不是通常的正面。 這有助於優化電源傳輸和信號路由,從而提高性能和密度。

Synopsys 補充說,其工具已通過臺積電的雲認證,以進一步簡化設計流程。 這使"共同客戶"能夠利用精確的雲 EDA 資源來完成綜合、定製佈局、仿真和籤覈驗證等任務。

在多芯片方面,Synopsys 的 3DIC Compiler 平臺通過與 Ansys 和臺積電的合作得到了增強。 3DIC Compiler 平臺基本上爲設計、實現和驗證複雜的 2.5D 和 3D 多芯片封裝提供了一個統一的環境。 在最新的更新中,它與 Ansys 的 RedHawk 籤核平臺緊密集成,執行熱分析和紅外感知時序分析。

值得一提的是,臺積電在去年的國際電子器件會議(IEDM)上也勾勒出了萬億晶體管芯片的路線圖,並在今年 5 月推出了另一個版本。 該公司將 2030 年作爲 1.4 納米 A14 和 1 納米 A10 工藝節點的目標。 與此同時,該公司還談到了開發 CoWoS、InFO 和 SoIC 等先進封裝技術。 這些技術將在 2030 年前後共同實現超過一萬億晶體管的巨型多芯片封裝。 隨着這一新消息的發佈,這家芯片製造商似乎離目標越來越近了。